炒股配资手机版 3D Chiplet,加速发展?

公开资料显示,贝特瑞是新能源材料的研发与制造商,主营业务包括锂离子电池负极材料、正极材料及石墨烯材料三大业务板块,是集基础研究、产品开发、生产销售于一体的国家级高新技术企业。

通用 Chiplet Interconnect Express (UCIe) 已发布“UCIe 2.0”。还新支持 3D 包装。尽管小芯片的概念已经存在很长时间了,但标准和工具在过去几年中已经开发出来。

管理小芯片技术的第二版标准已经到来。

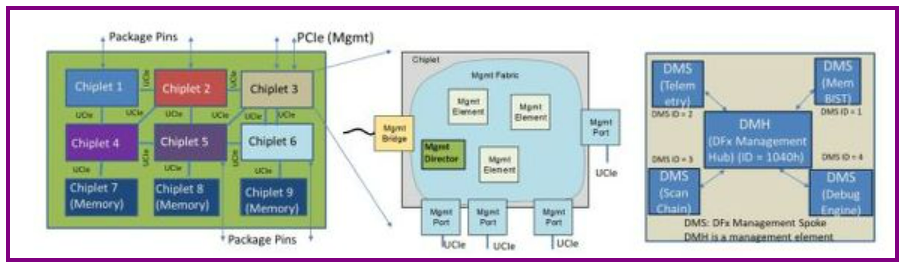

通用 Chiplet Interconnect Express (UCIe) 联盟成立于 2022 年 3 月,于 2024 年 8 月发布了“UCIe 2.0”规范。这些更新还解决了多芯片系统级封装 (SiP) 生命周期中的可测试性、可管理性和调试设计 (DFx) 挑战。UCIe 2.0 的一个关键特性是支持 3D(三维)封装,可显着提高小芯片带宽密度和功效。

UCIe 联盟主席 Debendra Das Sharma 在 EE Times 的简报中表示:“UCIe 2.0 规范完全向后兼容,并支持可选的管理功能和独立于供应商的小芯片互操作性。我们正在实施 UCIe DFx 架构 (UDA)。”。

该联盟正在将规范工作分配给多个工作组,重点关注不同方面,包括电气、协议、外形尺寸和合规性、可管理性和安全性以及系统和软件。达斯·夏尔马表示,最近成立的汽车工作组已开始收集要求,反映了汽车行业的兴趣。

“UCIe 1.0 是支持 2D 和 2.5D 的平面互连,这意味着小芯片是并排的,”他说,它支持 3D 堆叠,其中小芯片垂直堆叠。

Das Sharma 表示,UCIe 2.0 的其他重要更新与可管理性有关,包括封装后芯片底座和小芯片的调试和测试。UCIe 2.0 的另一个新功能是针对互操作性和合规性测试进行优化的封装设计。

UCIe 2.0 支持的管理机制包括小芯片及其配置的发现、电源和热管理、错误报告以及小芯片安全的各个方面。Das Sharma 表示,该机制利用了现有的适用行业标准,并且独立于小芯片上的底层协议。该机制还旨在与来自不同供应商的小芯片配合使用,并支持特定于供应商的扩展。

“UCIe 2.0”还考虑了混合键合的优化

l 转向混合键合是一种趋势

Das Sharma 表示:“小芯片的 3D 趋势之一是向混合键合发展,这种技术正变得越来越主流,并且可以大幅缩小小芯片之间的凸块间距。”由于 3D 互连实际上消除了小芯片之间的距离,因此互操作性必须限制在相同的凸块间距内。

UCIe-3D 针对凸块间距从 10-25μm 到小于 1μm 的混合键合进行了优化,提供了灵活性和可扩展性。

“互连距离短会影响电源效率,”达斯·夏尔马 (Das Sharma) 说道。“小芯片内部没有寄生效应,因此功耗显着降低。这是一个非常简单的电路,”他说。

Das Sharma 表示:“UCIe 追随 PCI Express 和以太网等更成熟互连的脚步,通过在优化能效的同时实现两位数的改进来提供更高的带宽密度。我的目标就是这一点。”

“在安全方面,UCIe 2.0采用中心辐射模型,以管理总监作为信任根。它增强了包级别的安全性,”他补充道。

l Chiplet 开始拥有标准和工具

Chiplet 技术并不新鲜炒股配资手机版,但近年来对实施该技术的最佳实践、标准和工具的需求不断增加。2022 年末,硅谷初创公司 Eliyan 走出隐秘模式,提供了一种更高效的封装方法。该公司的线束 (BoW) 小芯片系统使用标准封装来提供与采用先进封装技术的芯片到芯片实现类似的带宽、功率效率和延迟。

热点资讯

- 2024-08-11股票100倍杠杆 懂事的流浪狗不进入饭店里,只在门口等待投喂,被喂食物后好高兴

- 2024-10-03证券公司配资 港股异动 | 联想集团(00992)盘中涨超3% AI PC渗透

- 2024-08-07哪个平台可以买股票 四连板后净利预亏 东易日盛股价迎考

- 2024-09-26股票杠杆费用 #40岁以上女性禁用紧急避孕药##全民营养提升计划# 紧急避孕药,

- 2025-01-06跟私募做股票靠谱吗 2024年12月9日全国主要批发市场黄芪片(黄芪片直径1.0

- 2024-12-04资金杠杆股票 宁德时代第二代钠电池有望明年面世 能在极端严寒环境中工作

相关资讯

- 什么是金融杠杆炒股 去年国务院部门采纳代表委员建议五千余条,出台政策两千余项

- 福州股票配资开户 12月6日星球转债下跌0.47%,转股溢价率9.51%

- 炒股配资安全 泥塑大师张振福为台湾知名作家琼瑶塑肖像

- 配资资讯网 2024年10月5日海口市菜篮子江楠农产品批发市场有限公司价格行情

- 去杠杆与股市 中国移动负增长,收缩投资已成必然,5.5G或不会大规模建设